61. Filter used in switching regulators are also as called

A. DC – AC transformers

B. AC – DC transformers

C. DC transformer

D. AC transformer

62. Which of the following is considered to be the most important components of the switching regulator?

A. RC or RLC filter

B. RL or RLC filter

C. ORC or RL filter

D. RC, RLC or RL filter

63. Which are the most commonly used low voltage switching regulators?

A. Powdered Permalloy toroids

B. Fermite EI, U and toroid cores

C. Silicon steel EI butt stacks

D. None of the mentioned

64. Find the value of Rsc, L, and Co for a µA7840 switching regulator to provide +5 v at 3A, using the following specifications: toff= 24µs, ripple voltage = 400mA, and ton=26µs.

A. Rsc = 55 mΩ , L = 25µH & Co = 750µF

B. Rsc = 550 mΩ , L = 25µH & Co = 75µF

C. Rsc = 650 mΩ , L = 25µH & Co = 65µF

D. Rsc = 720 mΩ , L = 25µH & Co = 250µF

65. Calculate the efficiency of the step-down switching regulator has given the input voltage Vin= 13.5v and output voltage =6v. Assume the saturating Voltage Vs=1.1v and the forward voltage drop Vd = 1.257v

A. η = 75%

B. η = 48.5%

C. η = 63.9%

D. η = 80.5%

66. Match the characteristics of various switching regulators.

| Switching regulator | Characteristics |

| 1. Inverting | (i) [ton / toff ] = [ Vo + Vd] / [Vin -Vs -Vd]; Rsc = ( 0.33/ Ipk) |

| 2. step down | (ii) [ton / toff ] = [ Vo + Vd -Vin] / [Vin-Vs] ; Rsc = ( 0.33/ Ipk) |

| 3. step up | (iii) [ton / toff ] = [ Modulus Vo +Vd] / (Vin-Vs); Rsc = ( 0.33/ Ipk |

A. 1- iii , 2- i , 3- ii

B. 1- i , 2- ii , 3- iii

C. 1- iii , 2- ii , 3- i

D. 1- iii , 2- ii , 3- i

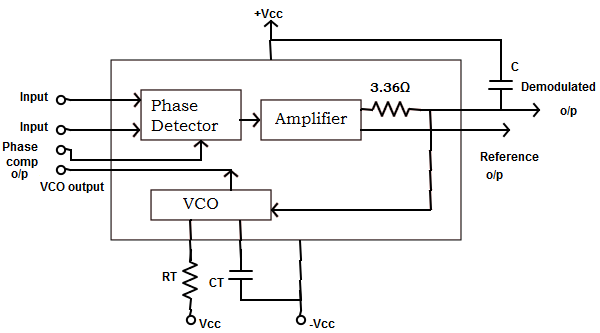

67. What is the conversion ratio of the phase detector in 565 PLL?

A. 0.14

B. 0.35

C. 0.4458

D. 0.7

68. Given fo = 1.2kHz and V = 13v, find the lock-in range of the monolithic Phase-Locked Loop.

A. ±575Hz

B. ±720Hz

C. ±150Hz

D. ±1kHz

69. A monolithic phase detector is preferred for critical applications as it is:

A. Independent of variation in amplitude

B. Independent of variation in the duty cycle of the input waveform

C. Independent of variation in response time

D. Both 1 and 2

70. Determine the capture range of IC PLL 565 for a lock-in range of ± 1kHz.

A. △FC = ±31.453Hz

B. △fc = ±66.505Hz

C. △fc = ±87.653Hz

D. None of the mentioned